Number Representation

People

Haohuan Fu, Oskar Mencer. Affiliates: Wayne Luk.

Main Publications

Haohuan Fu, Oskar Mencer and Wayne Luk, "Optimizing Logarithmic Arithmetic on FPGAs", to appear in Proc. IEEE International Conference on Field Programmable Custom Computing Machines (FCCM), Napa Valley, California, April 2007.

Haohuan Fu, Oskar Mencer and Wayne Luk, "Comparing Floating-point and Logarithmic Number Representations for Reconfigurable Acceleration", poster, Proc. Field Programmable Technology (FPT), 2006.

Altaf A. Gaffar, Oskar Mencer, Wayne Luk, Peter Y.K. Cheung, "Unifying Bit-width Optimisation for Fixed-point and Floating-point Designs", IEEE International Conference on Field Programmable Custom Computing Machines (FCCM), Napa Valley, California, April 2004 PPP.

Bit-width Analysis for Different Number Representations

We propose a method for the optimization of signal bit-widths for different number representation systems, thereby giving the designer the ability to explore the design space trade-offs when deciding which number representation would be the best choice for implementation.

A novel feature of this work is the use of automatic differentiation to compute the sensitivities of output to the precision bit-width of the internal signals. The proposed method was implemented within a compilation framework called BitSize (shown in the figure below), which targets re-configurable hardware architectures.

Application-specific Number Representation

Different from general processor platforms, FPGA enables application-specific number representations with customizable bit-widths.

Applicable number formats include regular representations like fixed-point and floating-point numbers, and irregular representations, such as Logarithmic Number System (LNS), Residue Number System (RNS) and some hybrid number systems. For different FPGA applications, selecting the proper number representation system is an important step that can greatly affect the performance and accuracy.

To select the optimal number representation system for reconfigurable applications on FPGAs, we develop a general comparison platform, which provides support for arithmetic units of different number systems and different bit-width settings.

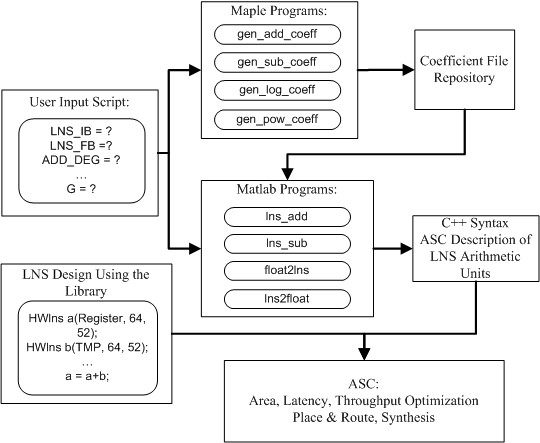

As our hardware design tool A Stream Compiler (ASC) already supports fixed-point and floating-point arithmetic, a major part of the work is the development of an LNS library generator.

The generator can automatically generate optimized LNS arithmetic units, especially LNS adders and subtractors, with a wide bit-width range from 21 to 64, which provide convenient support for LNS application development and design exploration.

RNS support is not included in the current work, but we plan to add RNS arithmetic libraries in the future work.

The figure above shows the general structure of the LNS arithmetic library generator. The Maple programs generate the coefficients and store them in the coefficient files. The Matlab programs read in the coefficient files and generate the hardware designs for LNS arithmetic functions, in the C++ syntax of ASC.

This project is funded by UK Engineering and Physical Sciences Research Council (grant number EP/C509625/1).